咨询电话

400-123-4567

手 机:13988999988

电 话:400-123-4567

传 真:+86-123-4567

邮 箱:admin@baidu.com

地 址:广东省广州市天河区88号

电 话:400-123-4567

传 真:+86-123-4567

邮 箱:admin@baidu.com

地 址:广东省广州市天河区88号

微信扫一扫

什么是IEEE 1801?

作者:365bet亚洲体育日期:2025/07/11 12:43浏览:

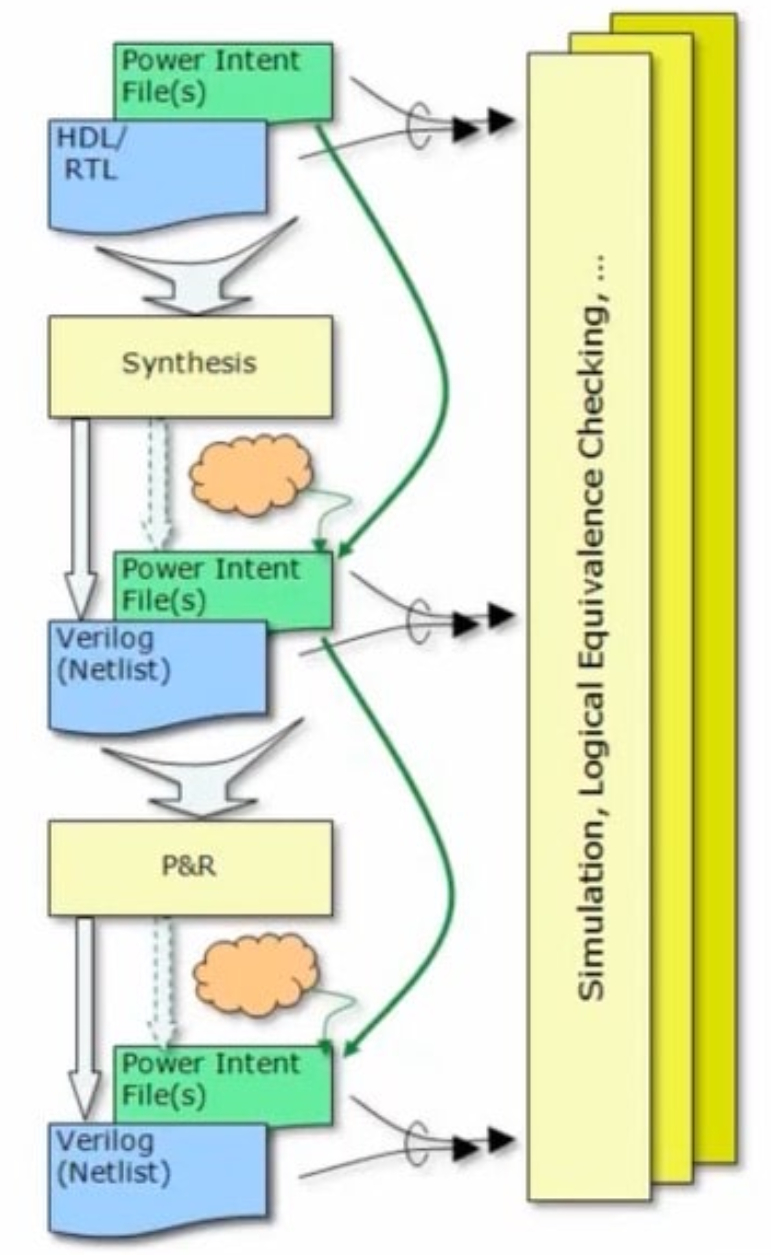

IEEE统一功率格式(UPF)4.0是一种标准规范语言,用于定义低功率ASIC的低功率体系结构。它着重于能源消耗电子系统设计的意图,并旨在简化整个设计,验证和实施过程的整合。 UPF是使用工具命令语言(TCL)创建的,并补充了硬件说明语言,例如SystemsVerilog和VHDL。这使设计人员可以指定基本的功率因素,例如功率域,能量状态,能量转换以及最大化低功率ASIC性能所需的其他因素。作为一种标准化的语言和框架,UPF承认EDA工具流中几种设计工具的可移植性和持续性能。 UPF功率奖励文件是在Diseño,验证和实施过程中使用的(图1)。以下是分组逻辑块,内存和其他被视为单个单元的组件出于能源管理目的。三个可能的状态定义了功率域。正常能量状态是一种低功率的状态,称为等待,不活跃或绘图,域暂时不活跃,但仍然保留它。域关闭且状态可能会丢失的其他状态是关闭或入睡。功率域是一个重要概念,用于定义能源的意图,并通过诸如电平转换器,绝缘单元和保留单元等功能来管理能量的一般消耗。 UPF定义用于连接不同电压域的电平转换器的位置和规格,从而允许另一个电压域正确解释电压域的信号。 UPF AIT添加了与绝缘单元的连接,以避免功率域和保留单元之间的意外能量泄漏,或者在断开能量时承认意外的记录以保持电源域的状态。宏用于捕获IN权力的方向和域的特征。他们承认IP的简化集成和重复使用。另外,在各种能源条件下验证设计所需的操作域条件也将详细说明(图2)。图2。IEEEEE1801UPF标准的重要元素。 (图像:Cadence)UPF 4.0引入了一些改进和新功能,以改善低功率的设计和验证。三个关键扩展是用于交换值转换表(VCT)的值转换方法(VCM),改进的保留建模和简化的宏。与VCT相比,VCM是UPF,具有模拟/混合信号设计中的MEJ性能,并且Power Network和HDL之间的转换提供了更丰富,更灵活的方法。 UPF 4.0结合了VCM和隧道,以将能量连接到各种类型的HDL,从而在整个设计和验证过程中提供了更一致的能源消耗意图。改进的保留建模包括对保存/恢复条件的更多控制,包括处理更复杂的配置,配置和保留关系的能力。储蓄/恢复条件的良好控制以及在保留组中考虑异步信号的影响的能力支持最精确的能量状态建模。新版本提出了优化的宏,简化了IP和设计优化的重复使用。简化的宏包括可变的终端限制,工具的强迫安全性和ACTSNON侵入性电源意图,可以在设计过程中进行系统级别的优化。它还承认上升设计验证,简化了IP模块的集成。 4.0的其他改进包括持续改进,以使设计更新更加有效。释放争议权的意图规格的优先规则是明确的,并提供了更一致,更可预测的行为ior。虚拟供应供应供应,以实质性供应的建模,从而简化了能量状态的定义。 UPF库通过改善设计用于重复使用的预定义电源意图的要素来加速设计过程。 IEEE UPF 4.0提供了一种标准化的方法,可以在低功率IC设计中编写和管理与能量相关的信息,从而助长了有意识的能源电子设备的发展。最新版本承认不同阶段和设计工具之间的合作更好,这使得更有效,更精确和可预测的低功率设计。

IEEE统一功率格式(UPF)4.0是一种标准规范语言,用于定义低功率ASIC的低功率体系结构。它着重于能源消耗电子系统设计的意图,并旨在简化整个设计,验证和实施过程的整合。 UPF是使用工具命令语言(TCL)创建的,并补充了硬件说明语言,例如SystemsVerilog和VHDL。这使设计人员可以指定基本的功率因素,例如功率域,能量状态,能量转换以及最大化低功率ASIC性能所需的其他因素。作为一种标准化的语言和框架,UPF承认EDA工具流中几种设计工具的可移植性和持续性能。 UPF功率奖励文件是在Diseño,验证和实施过程中使用的(图1)。以下是分组逻辑块,内存和其他被视为单个单元的组件出于能源管理目的。三个可能的状态定义了功率域。正常能量状态是一种低功率的状态,称为等待,不活跃或绘图,域暂时不活跃,但仍然保留它。域关闭且状态可能会丢失的其他状态是关闭或入睡。功率域是一个重要概念,用于定义能源的意图,并通过诸如电平转换器,绝缘单元和保留单元等功能来管理能量的一般消耗。 UPF定义用于连接不同电压域的电平转换器的位置和规格,从而允许另一个电压域正确解释电压域的信号。 UPF AIT添加了与绝缘单元的连接,以避免功率域和保留单元之间的意外能量泄漏,或者在断开能量时承认意外的记录以保持电源域的状态。宏用于捕获IN权力的方向和域的特征。他们承认IP的简化集成和重复使用。另外,在各种能源条件下验证设计所需的操作域条件也将详细说明(图2)。图2。IEEEEE1801UPF标准的重要元素。 (图像:Cadence)UPF 4.0引入了一些改进和新功能,以改善低功率的设计和验证。三个关键扩展是用于交换值转换表(VCT)的值转换方法(VCM),改进的保留建模和简化的宏。与VCT相比,VCM是UPF,具有模拟/混合信号设计中的MEJ性能,并且Power Network和HDL之间的转换提供了更丰富,更灵活的方法。 UPF 4.0结合了VCM和隧道,以将能量连接到各种类型的HDL,从而在整个设计和验证过程中提供了更一致的能源消耗意图。改进的保留建模包括对保存/恢复条件的更多控制,包括处理更复杂的配置,配置和保留关系的能力。储蓄/恢复条件的良好控制以及在保留组中考虑异步信号的影响的能力支持最精确的能量状态建模。新版本提出了优化的宏,简化了IP和设计优化的重复使用。简化的宏包括可变的终端限制,工具的强迫安全性和ACTSNON侵入性电源意图,可以在设计过程中进行系统级别的优化。它还承认上升设计验证,简化了IP模块的集成。 4.0的其他改进包括持续改进,以使设计更新更加有效。释放争议权的意图规格的优先规则是明确的,并提供了更一致,更可预测的行为ior。虚拟供应供应供应,以实质性供应的建模,从而简化了能量状态的定义。 UPF库通过改善设计用于重复使用的预定义电源意图的要素来加速设计过程。 IEEE UPF 4.0提供了一种标准化的方法,可以在低功率IC设计中编写和管理与能量相关的信息,从而助长了有意识的能源电子设备的发展。最新版本承认不同阶段和设计工具之间的合作更好,这使得更有效,更精确和可预测的低功率设计。相关文章

- 2025/09/07深度!该国最重要的武器Dongfeng说:“罢

- 2025/09/06CNN:美国崩溃了!

- 2025/09/05“黑色辛辣的眼睛”被广东的Chintan抓住,

- 2025/09/04土耳其超级联赛冠军可以签下两名曼联守